| << Chapter < Page | Chapter >> Page > |

A number of apparently inoffensive assumptions were made in the development of the tradeoff formulas used in the previous examples. One was that one-step (also called single stage ) decimation is used in the tuner's filtering and the other is that the number of multiplications and additions forms good basis for comparing the complexity of various designs. This example demonstrates some counterexamples along the way to the description of a system that represents the current state of the art (circa 1990) in tuner and transmultiplexer design.

Suppose that our goal is to accept a full 2700-channel FDM telephone baseband, select an FDM group with a tuner, and then demultiplex the constituent 12 voice grade channels with a transmultiplexer. In the now-familiar way, we develop the certain specifications for the transmultiplexer and tuner separately and then jointly optimize the shared parameters.

We now turn to [link] to determine the optimum value of f s , and with it, , and N . Plugging in to this equation yields an optimal f s of about 490 kHz, more than ten times greater than the FDM group's bandwidth. In analyzing this result, we find that the amount of computation needed by a single-step FIR decimating tuner is so high that it dominates that needed by the transmultiplexer. Clearly another approach is needed.

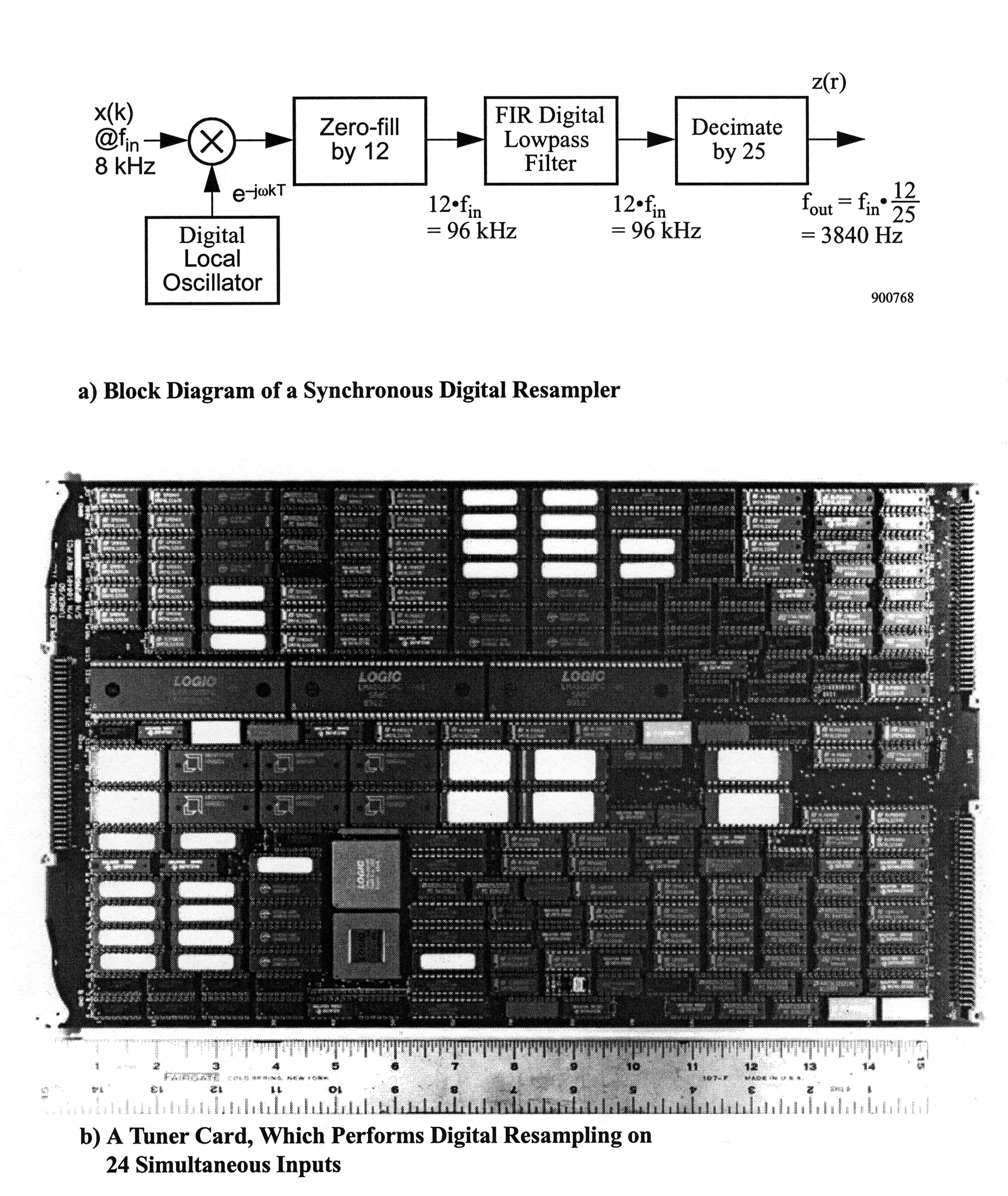

In response to this problem, the company developed a pair of custom application-specific ICs (ASICs) for selecting FDM groups from digitized basebands and another chip for transmultiplexing four FDM groups. The block diagram is essentially the same as that shown in Figure 1 from "Derivation of the equations for a Basic FDM-TDM Transmux" except that a multistage decimating filter is used. In all, nine filter stages are employed. Each bandlimits the incoming signal sufficiently that a decimation by two is possible. The first few stages, the ones that must operate at very high rates, use pulse responses so simple (for example, ) that only shifting and addition are needed. The effect of nine divisions by 2 is the reduction of the sampling rate f s to 64 kHz. The 48-kHz-wide FDM group is thus represented at the output of the tuner chips as complex-valued samples at a rate of 64 kHz.

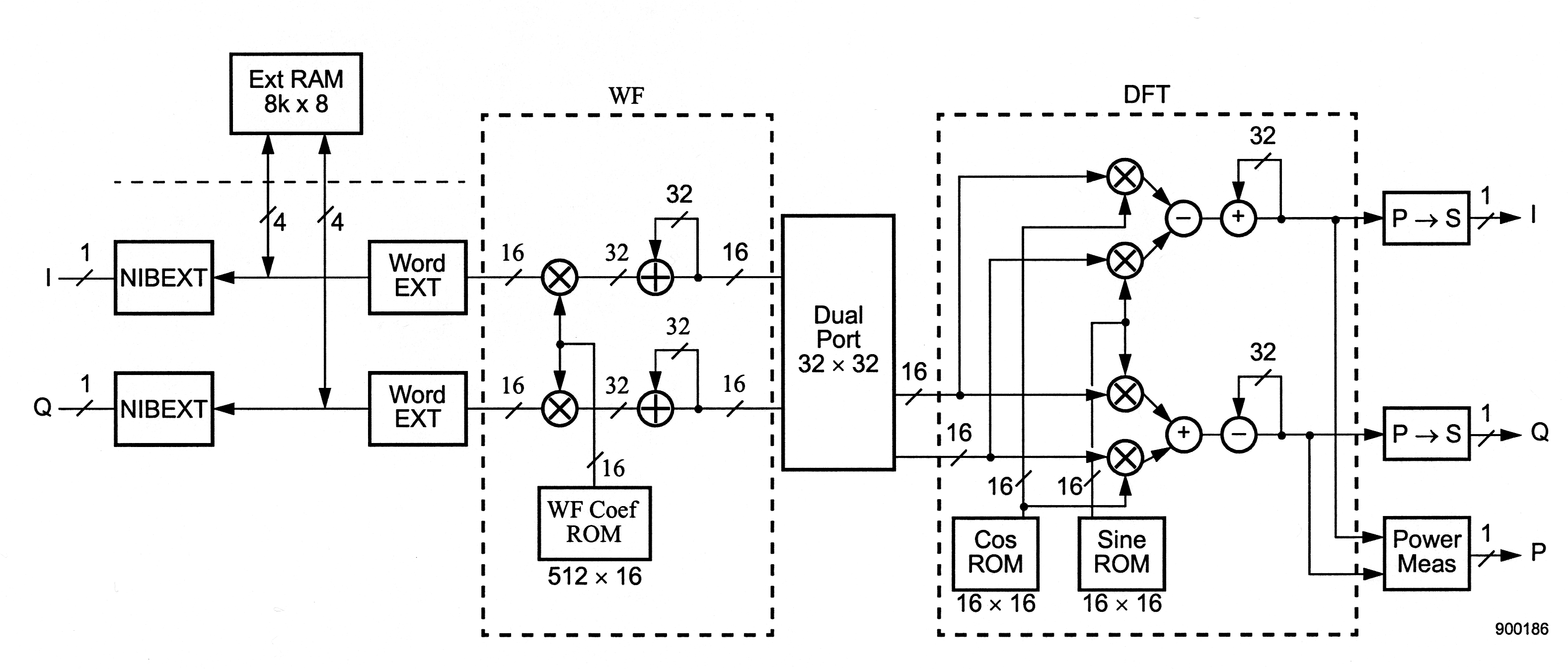

The transmultiplexer ASIC accepted four FDM groups, each quadrature-sampled at 64 kHz, and demultiplexes all 48 voice grade channels. A block diagram of a single path through the device is shown in [link] . The window-and-fold circuit was implemented by using onboard weighting coefficients and serial multipliers. The partial sums were stored in off-chip RAM. The output of the window-and-fold circuit was then transformed using a 16-point DFT. The complex-valued bin outputs, produced at a 4 kHz rate, were sent out over a serial interface.

Several of the design choices made with these chips are different that those seen earlier in the technical note. The first, seen in the tuner chips, is the use of multistage decimation. As [link] shows, this can almost always reduce the total amount of multiply-add computation needed for the tuner, at a certain cost in design simplicity. The other issue, evident in the design of both the tuner and the transmultiplexer, is that memory and control are at least as costly commodities in an ASIC design as are multiplications and additions. A vivid example is that the transmux ASIC used direct computation of the DFT rather than using an FFT. Even though the amount of multiplication is on the order of four times as much using the DFT, the overall DFT design used less silicon than the equivalent FFT.

Notification Switch

Would you like to follow the 'An introduction to the fdm-tdm digital transmultiplexer' conversation and receive update notifications?